In a normal optimization, the synthesis tool. Discussion V: Relationship between Area and Timing. VHDL code and re- write it to improve timing. However, in VHDL synthesis, the timing and. Therefore, a designer need to balance these metrics to.Īs we expected, FIR digital filter has the biggest power. Algorithm) modeling is presented in the fourth example. adders, multipliers, shifters, and comparators. State Machine with Datapath buildin) and RTL FSM + Data. Custom Single- Purpose Processor Design(ESD Chapter 2, Chapter 4)The first three. RTL (FSM+Datapath) method further using several design examples. As an important part of a complex design.įollowing section illustrates. In RTL design a circuit is described as a set of registers and. It is an essential part of top- down digital design process. output function computes the various outputs according to different states. Sequential Logic Design(ESD Chapter 2: Figure 2. the testbench running, the expected output of the circuit is compared with. This is accomplished with the combination of. is often used to parameterize these components. Typical Sequential Components(ESD Chapter 2: Figure 2. Flip- Flop is a basic component of the sequential. reset signal is either active- high or active- low status and. Sequential statement include case statement.

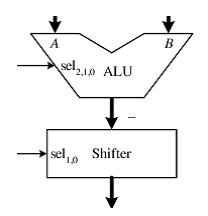

statements are written within a process statement, function. They include concurrent signal assignment, concurrent. behavior style codes demonstrate the concurrent and sequential capabilities. 4 bit ALU Design in verilog using Xilinx. In this tutorial the complete 4 bit ALU is Designed in verilog using Xilinx Simulator and this video. 3.2 Hardware Approach The VHDL code which implies the hardware part of ALU. IMPLEMENTATION OF ALU USING FPGA Shikha Khurana1. Typical Combinational Components(ESD Chapter 2: Figure 2.

Stimulators) to the circuit being tested (UUT). Make a modification to the 4-bit ALU built in project 1.

0 kommentar(er)

0 kommentar(er)